打开文本图片集

摘 要:本文应用等精度测量法,提出了一种宽带小信号数字频率计的设计方案,满足10KHz~100MHz带宽内万分之一的频率测量精度。模拟信号通过OPA691放大器宽带放大、TLV3501高速整形,进入FPGA进行等精度数字频率测量,测量结果通过总线传送给STM32系统显示,系统在带宽范围内均达到了测量精度要求。测频核心程序用Verilog语言编写,并给出了模块设计及测量结果。整个系统具有成本低廉、简单实用、测量精度高的优点。

关键词:数字频率计;等精度测量法;OPA691;宽带放大

中图分类号:TP311 文献标识码: A 文章编号: 2095-8595 (2016) 06-685-04电子科学技术 URL: http//.cn DOI: 10.16453/j.issn.2095-8595.2016.06.004

引言

频率是研究领域中最重要的参数量之一,数字频率测量指标更是通信领域/电信领域研究、设计/调试电路中最重要的指标之一。然而在谐振法、外差法、示波法等数字频率计的传统设计方法中,当遇到大宽带测量时,测量很难在带宽内均保持满意精度。为解决这一问题,本设计应用等精度测量法,提供了一种将正弦波小信号放大、整形的数字频率测量系统。该系统具有成本低廉、效率高的优势。

1 等精度测量法分析

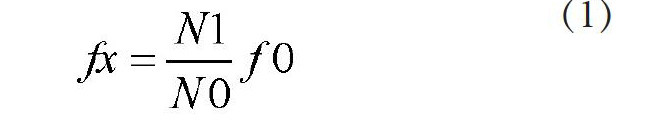

在数字测量频率的方法中,经典的标准频率比较测量法简单易行,但在高频下精度不高。它使用两组计数器,在相同的门限时间(闸门时间)内同时计数,测得待测信号的脉冲个数为N1,已知标准信号的脉冲个数为N0,已知标准信号的频率为f0,则设待测信号频率为fx,理论上可得到等式N1/fx=N0/f0;继而可以求出:

标准频率比较法的缺点是输入信号与时钟信号不同步,在高频下测量的±1误差很容易导致测量精度不高。等精度测量法则是基于标准频率比较法,为提高测量精度做了改进。

等精度测量法,让闸门时间信号通过同步触发器与输入信号同步。同步后的闸门时间控制计量:当闸门门限上上升沿到来时,如果待测信号的上升沿没有到来时,两组计数器不计数,只要待测信号上升沿到来,两组计数器就开始计数。当闸门门限下降沿到来时,如果待测信号的一个周期没有结束,两组计数器计数不停止,一旦待测信号记够一个周期,计数器计数停止。这样±1误差就被均摊到同步后的整个闸门时间内,从而减小误差,提高了测量精度。

如图1所示:闸门时间T1与外部的被测信号同时进入D触发器中同步,得到新的闸门时间T(T略大于T1,是外信号的整数倍周期),在时间T内,控制门打开、两组计数器分别对待测信号fx和时钟信号f0的周期分别计数为N1和N0。由公式(1)可求待测频率fx。

因为闸门时间与被测信号fx是同步的,所以就导致了闸门时间T1与T是不相等的,所以在T内对时钟信号周期计数,来确定时间T的大小。也正是因为闸门时间与被测信号同步,所以fx测量不存在±1误差,但是时钟信号f0和门限时间T不同步,所以f0测量存在±1误差,但被均摊到同步后的整个闸门时间内,对频率测量影响很小,因此提高了测量精度。

2 系统的整体设计方案

宽带数字频率计主要由宽带小信号放大电路、高速整形电路、FPGA频率测量系统和STM32显示组成。其中宽带小信号放大电路是由芯片OPA691组成的放大电路将小信号正弦波进行放大。高速整形电路是由TLV3501组成施密特触发电路对进过宽带小信号放大电路的正弦波信号进行波形整形成方波信号。FPGA频率测量应用等精度测量法对通过模拟链路的待测信号进行频率计数,计数后的信号进入STM32进行进制转化及数字显示,宽带小信号数字频率计系统的整体设计方案如图3。

2.1 宽带小信号放大电路设计

本设计给的输入信号为10KHz~100MHz的正弦波宽带小信号。所以需要通过放大电路及波形整形电路后在进入FPGA中。放大电路设计,采用的是TI公司的OPA691芯片,该芯片是宽带电流型放大芯片,根据数据手册可以知道此芯片在放大10倍时,带宽可以达到200MHz,输入偏移电压值仅有500μV,并且芯片的转换速率高达2100V/μs,是一款性价比很高的芯片[3]。所以根据此芯片数据手册设计宽带小信号放大电路如图4。

高速波形整形电路是通过使用芯片TLV3501设计,TLV3501芯片是一款有4.5ns的轨到轨高速输出比较器[4],通过TLV3501芯片搭成单电源供电的施密特触发器根据其数据手册和比较器计算公式

设计电路如图5,并可以计算出通过施密特触发器的触发电平分别是0.25V和2.75V[5]。可以使FPGA正常工作。

2. 2 FPGA频率测量设计

FPGA频率测量设计的FPGA软件主要应用了状态机设计,并且很好的运用了模块化思想。FPGA频率测量系统中主要应用了等精度测量法进行频率测量,其中包括被测信号频率计数器、内部时钟计数器、1s闸门门限计数器及锁存器等模块。

FPGA频率测量程序的主要設计思路就是等精度测量法,当正弦波小信号经过放大整形后的被测信号进入FPGA中,本地100MHz时钟信号通过周期计数获得标准1s闸门时间信号T1,与被测信号fx同时进入同步D触发器中(信号T1进入D端,信号fx进入CLK端),从而获得与被测信号同步闸门时钟信号T,当同步后的闸门时间信号T上升沿到来时,使能端变为高电平1,使两组计数器开始分别计100MHz时钟信号与被测信号周期次数,在下降沿到来时,使能端变为低电平0,两组计数器停止计数并将两组计数器所计周期数保持锁存,在新的一轮闸门信号到来时计数器清零重新开始计数。整个FPGA测量过程画状态迁移图如图6。

2. 3 STM32显示设计

信号通过FPGA频率测量后,输出的信号是周期数,所以需要通过STM32根据公式(1)将FPGA频率测量系统中的输出信号进行转化,从而得到被测信号频率值。并通过STM32将频率在显示屏上进行显示。

3 系统实测

测试条件和仪器分别如下:

测试条件包括:±5V直流电压源;0 dbm的射频输入正弦波信号;频率10KHz~100MHz的随机射频输入正弦波信号。

测试仪器包括:安捷伦高频DSO7054示波器、安捷伦高频N9310A信号发生器。

3.1 模拟链路系统测试结果

从图7可以看出比较器在10KHz时工作良好,正弦波信号经过两级放大后,饱和失真,最高电压可以达到触发电压值,上升沿与下降沿不存在噪声的干扰,可以保证信号进入FPGA后FPGA计数的准确性。由于链路连接的延时,使得两信号有一定的相差。

从图8可以看出比较器在100MHz时工作良好,正弦波信号经过两级放大后,饱和失真,最高电压可以达到触发电压值,上升沿与下降沿不存在噪声的干扰,虽然信号失真严重,但是不影响信号进入FPGA后FPGA计数的准确性。由于链路连接的延时,使得两信号有一定的相差。

3.2 数字频率计整体系统测试结果

测试结果如表1所示。

从表1可知,该系统可以满足小信号10KHz~100MHz的高带宽高精度频率的测量。

4 结语

以OPA691组成的宽带小信号放大电路以及TLV3501组成的高速整形电路所构成的模拟链路系统与FPGA频率测量系统及STM32显示系统形成的数字频率计的系统设计可以测量10kHz~100MHz的频率,并且精度达到了万分之一。在调试中我们也遇到了各种各样的问题,比较器连接FPGA的地方的电容导致了高频率达不到,通过改变分压电阻阻值解决,还有通过改变高速整形电路的触发电压减小噪声对频率测量的影响等。此方案还可以继续研究,进行相位差的测量,值得深入的研究。

致谢:

本课题受到北方工业大学学生科技活动项目、北京市大学生科学研究与创业行动计划项目的资助与支持。

参考文献

黄争,李琰.运算放大器应用手册——基础知识篇[M].电子工业出版社.

TI公司.德州仪器半导体技术(上海)有限公司大学计划. 德州仪器高性能模拟器件高校应用指南, 2013,08.

TI公司.OPA691 Datasheet.OPA691.pdf.

TI公司.TLV3501 Datasheet.TLV3501.pdf.

童詩白,华成英.模拟电子技术基础[M].高等教育出版社,2006.

ADI中文技术论坛.杨建国.西安交通大学. 你好,放大器.2014. https://ezchina.analog.com/community/amplifiers