打开文本图片集

摘要:介昭了一种基于FPGA的图像处理系统设计,该系统主要由视频图像采集和图像压缩两部分组成,实现了对网络图像进行采集和压缩的功能。本文采用自顶向下的设计方法完成了整个FPGA的逻辑设计,为了简化系统,采用了Altera公司提供的IP软核。完成系统整体设计后,对各模块功能及系统整体进行验证,分析了各模块的逻辑功能合理性和系统整体的时序正确性。

关键词:FPGA 图像采集 图像压缩 网络传输

中图分类号:TP274 文献标识码:A 文章编号:1007-9416(2016)06-0165-02

随着人们对安全的需求日益强烈,视频监控系统作为一种安全防范的手段,越来越受到广泛的关注。在视频监控系统中,视频图像的采集、压缩机传输质量直接影响系统的监控质量,因而,高保真准动态图像的采集、压缩和远程传输技术成为许多先进国家计算机领域的重要研究课题,研究网络图像采集及压缩处理技术具有重大的现实意义。由于FPGA在流水线并行处理数据上具有强大优势,具有集成度高,体积小,可灵活配置等优点,在图像处理领域得到广泛应用。本文介绍一种基于FPGA实现图像采集及压缩的设计方案、以便于图像的网络传输。

1 系统总体设计

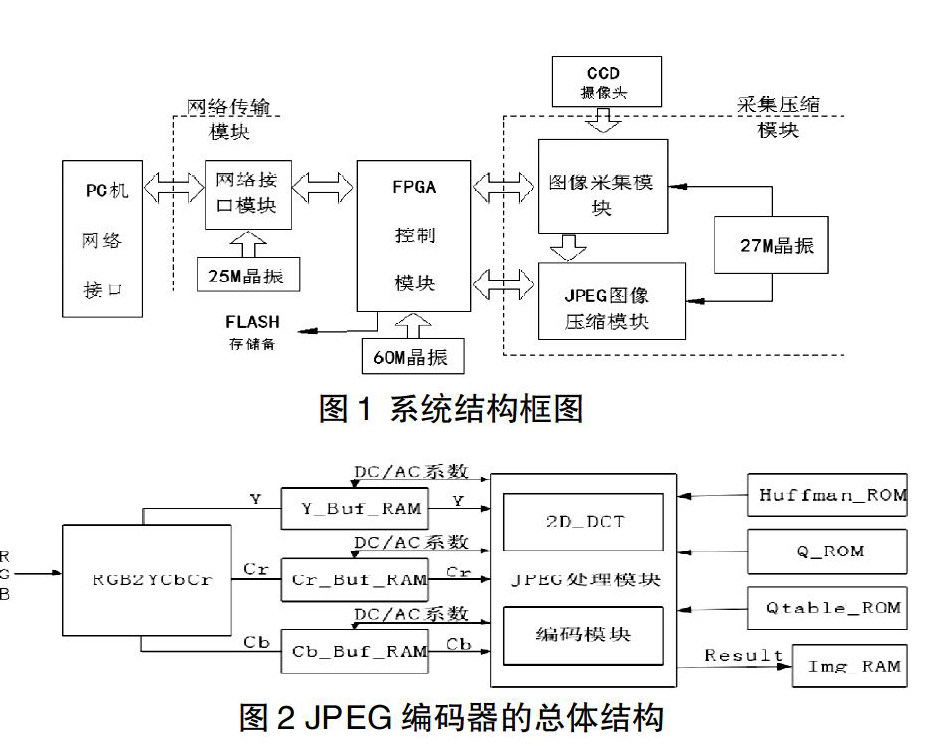

本文设计了一种能实现对图像进行实时采集和实时压缩的图像采集与压缩系统,系统的总体框图如图1所示。该系统主要包括视频图像采集模块、图像压缩模块、逻辑控制模块和网络传输模块。其中,图像的采集由图像采集模块完成,该模块将CCD摄像头输入的PAL制式模拟视频图像转换为标准的ITU-R BT.656 YCbCr4:2:2格式的8比特视频数据进行输出;采集到的图像经过A/D转换成数字信号后需要进行压缩从而进行网络传输,图像的压缩由图像压缩模块按 JPEG标准完成压缩;FPGA逻辑控制模块负责各个芯片之间的时序匹配、发生以及各芯片工作模式和某些工作参数的初始化配置,同时还协调网络传输接口的数据读写;数据传输模块负责将压缩后的图像数据通过网络接口传送到PC。

2 图像采集模块硬件设计

2.1 工作原理

本文设计的视频图像采集模块主要由三部分组成,分别是:图像获取部分、解码芯片部分和FPGA部分。图像获取选用CCD图像传感器,解码芯片选择美国AD公司的ADV7180,FPGA芯片选用Altera公司的CyelonelI系列EP2C35F484C8。该模块的工作原理是:CCD摄像头输出的视频信号经过ADV7180芯片解码,输出符合ITU-R BT.601标准的数据流。具体步骤为:首先从CCD摄像头获得 PAL制模拟视频信号;然后将该模拟信号通过 ADV7180芯片将其变换为数字信号,ADV7180上电后需要先进行初始化配置才能采集模拟视频信号并进行 A/D转换。

2.2 解码芯片ADV7180

ADV7180是美国AD公司的一款多功能数字视频解码芯片,它可以自动检测到兼容国际标准的NTSC、PAL和SECAM制式的模拟视频基带信号,并自动进行识别,然后将它们转换成标准的ITU-RBT.656YCbCr4:2:2格式的8比特视频数据。通过设置工作模式,ADV7180可支持27MHz时钟频率下CVBS(composite)、YPrPb(Component)或Y/C(S-Video)格式的视频信号输入。ADV7180的内部集成3 个86MHz、10 位的 ADC,具有 5 行色度梳妆滤波器,6路模拟输入信道,这6 路模拟视频输入通道支持三种输入模式: CVBS、Y/C 和 YPrPb。

2.3 硬件电路设计

为保证输入的音频信号在ADC的允许范围内(0V~1V),视频信号在进入ADV7180之前需要加一个电压分离网络。ADV7180的功能和状态由内部控制寄存器来进行设置和查询,其初始化配置由FPGA编程实现。ADV7180 在完成内部寄存器初始化以后,开始接收模拟视频信号并按预先设定好的模式开始工作,其输出的数字视频信号为符合8-bitITU-RBT.656YCbCr4:2:2协议标准的格式,该接口协议为数字视频接口标准,主要用于数字视频设备之间采用27MHz/s并口或243Mb/s串行接口的数字传输接口标准。ADV7180

的输出是并口模式,对外接口主要包括四路同步信号和一路并行图像数据(格式为标准的8比特视频数据),这四路同步信号分别是:帧同步信号、场同步信号、行同步信号和同步时钟信号。经ADV7180解码后的视频信号若想由图像处理芯片完整无误地恢复出原来的视频图像数据,则需要保持正确的时序对应关系。

3 图像压缩模块硬件电路设计

3.1 图像压缩JPEG编码器设计

本设计对JPEG编码算法采用自顶向下的设计方法,将JPEG编码系统分成四个模块:颜色空间转换模块、二维DCT模块、JPEG的编码模块和存储器模块,这四个模块分别复用不同的IP核,各模块关系如图2所示,图中的箭头表示数据流向。

3.2 图像采集压缩系统的网络应用

本系统对视频图像压缩之后通过以太网进行网络传输。以太网是一种遵守802.3协议的局域网,通过数据链路层实现网络传输。网络传输接口模块采用台湾DAVICOM公司的一款高速以太网控制芯片DM9000A。其工作原理是:当DM9000A接收到外部网络送来的以太网数据时,先检查数据帧的合法性,如果数据帧合法则将其存到内部SRAM中,通过中断命令实现将DM9000A接收SRAM的数据读出并进行处理。

FPGA控制DM9000A的初始化和数据的接收和发送。共分为三个部分:首先是DM9000A的初始化,然后是数据的发送过程和数据的接收过程。初始化过程是:DM9000A的初始化由FPGA通过总线配置其内部寄存器而完成。数据接收过程是:初始化完成之后进入数据收发等待状态,当外部网络送来以太网数据时,一旦DM9000A接收到以太网帧,FPGA即将相应的数据从DM9000A的接收FIFO读出。数据发送过程是:若需要向外发送数据,则由FPGA启动以太网发送程序,然后将解调数据发送到DM9000A中来完成。

4 测试结果与分析

为了验证整个系统的工作特性,用CCD摄像头在校园里拍了一副图片,如图3所示,图像的分辨率为352×288。将该图按照不同压缩比例进行了两次压缩处理,压缩比例及压缩质量参数如表1所示,压缩之后的图像如图4和图5所示。

图4和图5分别表示了被压缩的源图像经过本系统压缩处理后的图像,这两幅图表明本文设计的基于FPGA的图像采集与压缩系统能实现既定的功能,验证了系统设计的正确性和可行性。同时,从这两幅图可以看出,图4的压缩质量比图5的压缩质量高,JPEG压缩算法的图像压缩质量主要由压缩时选择的量化表而决定,当量化表中的步长越小,压缩比就越小,图像质量就越高,这一特性与表1中的参数吻合。这一实验结果表明,在利用JPEG算法进行图像压缩时,可通过选择合适的量化步长来制定量化表,从而得到压缩比和图像质量均满意的效果。

5 结语

本文介昭了一种基于FPGA的图像采集与压缩系统设计和实现方法。系统主要包括图像采集模块、图像压缩模块和网络传输模块。在FPGA上实现图像采集、视频压缩和线路编码解码,利用FPGA并行处理优势大大提高了系统的处理速度。该系统具有结构简单,高集成度、低功耗、低成本,以及运行速度快等优点。通过测试该系统可以稳定高效的工作,达到高清图像采集和压缩的要求,可广泛应用于校园、社区和工业园等,具有较高的实用价值。

参考文献

[1]贺永波.基于USB2.0的高速图像采集系统设计.华中科技大学硕士学位论文.武汉:华中科技大学,2006.

[2]张晓飞,袁祥辉.基于DSP成像系统的视频图像采集部分的实现.压电与声光,2002(6).

[3]杜林奇,许开宇,张欣璐.基于FPGA和视频解码芯片的实时图像采集系统设计.电手元器件主用.2008,10(5).

[4]刘芳敏,吴永辉,俞建新.JPEG2000 图像压缩过程及原理概述[J].计算机辅助设计与图形学学报,2002(10).

[5]饶兴.基于Huffman编码的图像压缩解压研究[J].电脑知识与技术,2011(4).